LA FlipFlop

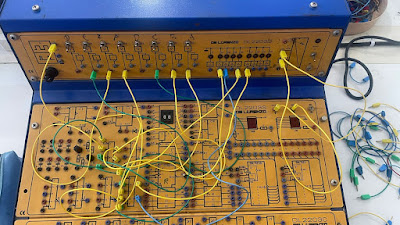

Pada rangkaian ini, kita menggunakan Modul d'Lorenzo dengan konfigurasi sebagai berikut:

- Input B0 dihubungkan ke input R pada J-K dan D Flip Flop.

- Input B1 dihubungkan ke input S pada J-K dan D Flip Flop.

- Input B2 dihubungkan ke input J pada J-K Flip Flop.

- Input B3 dihubungkan ke input CLK pada J-K Flip Flop.

- Input B4 dihubungkan ke input K pada J-K Flip Flop.

- Input B5 dihubungkan ke input D pada D Flip Flop.

- Input B6 dihubungkan ke input CLK pada D Flip Flop.

Selanjutnya, VCC dan ground disambungkan untuk memastikan rangkaian memiliki sumber daya yang diperlukan untuk beroperasi.

1. D Flip Flop

Pada rangkaian D flip flop, seperti terlihat pada gambar di sisi kiri, kita perhatikan terlebih dahulu input S dan R karena keduanya adalah input prioritas. Input S dan R bersifat active low, yang berarti akan aktif jika diberi nilai 0. Namun, dalam kondisi ini, input yang diberikan adalah 1, sehingga kita dapat mengabaikan input S dan R dan fokus pada input di kaki D dan clock. Output dari rangkaian ini akan mengikuti tabel kebenaran D Flip Flop.

2. J-K Flip Flop

Pada rangkaian J-K flip flop, seperti terlihat pada gambar di sisi kanan, pertama-tama kita periksa input S dan R karena keduanya merupakan input prioritas. Input S dan R bersifat active low, sehingga akan aktif saat diberi nilai 0. Namun, dalam kondisi ini, input yang diberikan adalah 1, sehingga kita bisa mengabaikan input S dan R dan fokus pada input di kaki J, K, dan clock. Output dari rangkaian ini akan mengikuti tabel kebenaran J-K Flip Flop.

-

· J = 0, K = 0: Hold (Q tidak berubah).

· J = 0, K = 1: Reset (Q menjadi 0).

· J = 1, K = 0: Set (Q menjadi 1).

· J = 1, K = 1: Toggle (Q berubah dari 0 ke 1 atau 1 ke 0).

- Baris 1 (Input: B0 = 0,B1=1 B2-B6=X)

· Pada kondisi ini, B0 bernilai 0,B1=1 sementara B2 sampai B6 ditandai dengan "X" (don’t care atau tidak diperhatikan).

· Output J-K Flip-Flop: Q=0 Q’=1.

· Output D Flip-Flop: Q=0 Q’=1.

· Penjelasan: Ketika B0 adalah 0, baik J-K maupun D flip-flop berada pada kondisi reset, sehingga Q tetap pada 0 dan Q’ pada 1.

- Baris

2 (Input: B0 = 1, B1=0 B2-B6=X)

· Output J-K Flip-Flop: Q=1 Q’=0.

· Output D Flip-Flop: Q=1 Q=0.

· Penjelasan: Ketika B0 bernilai 1, baik J-K maupun D flip-flop berada dalam kondisi set, sehingga output Q menjadi 1 dan Q’menjadi 0.

- Baris

3 (Input: B0-B1 = 0,B2-B6=X )

· Output J-K Flip-Flop: Q=1 Q’=1.

· Output D Flip-Flop: Q=1 Q’=1.

· Penjelasan: Pada kondisi ini, flip-flop tetap berada pada set sehingga Q tetap pada 1 dan Q’ 1.

- Baris

4 (Input: B0-B1 = 1, B2 = 0,B3=CLK B4-B5=1)

· Output J-K Flip-Flop: Q=0 Q’=1.

· Output D Flip-Flop: Q=1 Q’=0.

· Penjelasan: Ketika B2 adalah 0 dan B0 1, flip-flop beralih ke kondisi reset, sehingga Q menjadi 0.

- Baris

5(Input: B6 = 0, B5 = X, B0-B1 = 1,B2=0 B3=CLK B4=0)

· Output J-K Flip-Flop: Q=0 Q’=1.

· Output D Flip-Flop: Q=0 Q’=1.

· Penjelasan: Kombinasi input ini membuat J-K dan D flip-flop tetap pada kondisi reset dengan Q di 0.

- Baris

6 (Input: B0-B2=1 B3=CLK B4=0 B5=X B6=0)

· Output J-K Flip-Flop: Q=1 Q’=0.

· Output D Flip-Flop: Q=1 Q’=0.

· Penjelasan: Kondisi ini menyebabkan flip-flop berada pada set dengan output Q 1.

- Baris

7 (B0-B2=1,B3=CLK,B4=1 )

· Output J-K Flip-Flop: Ditandai sebagai "toggle" untuk Q dan Q’

· Output D Flip-Flop: Tidak ada perubahan yang signifikan; D flip-flop tidak memiliki mode toggle sehingga output tetap stabil.

· Penjelasan: Pada baris ini, J-K flip-flop dalam mode toggle. Mode toggle pada J-K flip-flop terjadi saat kedua input J dan K bernilai 1, di mana output akan berganti-ganti antara 0 dan 1 pada setiap siklus clock.

- Baris

1 (Input: B1 = 1, B0 = 0,T=X)

·

Pada kondisi ini, T flip-flop mendapatkan PRE

(Preset) aktif (1) dan CLR (Clear) aktif (0), yang artinya flip-flop berada

pada kondisi reset.

·

Output: Q=0 Q=1.

·

Penjelasan: Karena CLR aktif (0), flip-flop akan

di-reset sehingga output Q menjadi 0 dan Q’ menjadi 1.

- Baris

2 (Input:B2=X B1 = 0, B0 = 1)

·

Pada kondisi ini, PRE Preset) tidak aktif (0)

dan CLR aktif (1), yang mengindikasikan bahwa flip-flop akan berada dalam

kondisi set.

·

Output: Q=1 Q’=0.

·

Penjelasan: Karena PRE aktif (0), flip-flop

di-set sehingga Q menjadi 1 dan Q’ menjadi 0.

- Baris

3 (Input: B2= X B1= 0, B0 = 0)

·

Pada kondisi ini, baik PRE (Preset) maupun CLR

(Clear) tidak aktif (0), sehingga tidak ada perubahan pada output.

·

Output: Q=1 Q’=1.

·

Penjelasan: Karena PRE dan CLR tidak aktif,

flip-flop menahan output sebelumnya. Dalam hal ini, Q tetap 1 dari kondisi

sebelumnya.

- Baris

4 (Input: B2 = CLK, B1 = 1, B0 = 1)

·

Pada kondisi ini, input T berada dalam mode Clock(1),

dan PRE serta CLR keduanya aktif (1), yang memungkinkan flip-flop untuk

beroperasi dalam mode toggle.

·

Output: Toggle antara Q dan Q’.

·

Penjelasan: Karena T berada di kondisi CLOCK,

flip-flop akan berada dalam mode toggle, yang artinya output Q akan beralih

dari 0 ke 1 atau sebaliknya pada setiap siklus clock. Hal ini mengubah keadaan

Q di setiap siklus, sehingga Q dan Q’terus beralih antara 1 dan 0.

T flip-flop pada tabel ini menunjukkan bahwa saat PRE atau

CLR aktif, flip-flop akan berada dalam kondisi set atau reset sesuai sinyal

yang diterima. Ketika keduanya tidak aktif, flip-flop akan menahan output

sebelumnya. Namun, saat T berada dalam mode toggle (1) dan PRE serta CLR

keduanya aktif (1), T flip-flop akan beralih (toggle) di setiap siklus clock,

membuat output Q dan Q’ bergantian secara terus-menerus.

Komentar

Posting Komentar