Percobaan 1 Kondisi 2

Buatlah rangkaian J-K flip flop dan D flip flop seperti pada gambar pada percobaan dengan ketentuan input B0=0, B1=1, B2=don’t care, B3=don’t care, B4=0, B5=don’t care, B6=clock

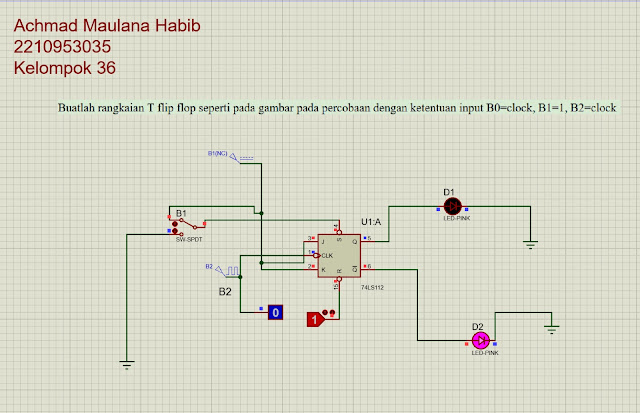

Percobaan 2 Kondisi 19

Buatlah rangkaian T flip flop seperti pada gambar pada percobaan dengan ketentuan input B0=clock, B1=1, B2=clock

2. Gambar Rangkaian Simulasi[Kembali]

Gambar 1.Percobaan 1 Kondisi 2

Gambar 2.Percobaan 2 Kondisi 19

Rangkaian 1

Flip-flop JK bekerja berdasarkan logika JK:

- Jika J = 0 dan K = 0, maka output Q tidak berubah (tetap sama).Jika J = 0 dan K = 1, maka output Q akan reset (Q = 0).

- Jika J = 1 dan K = 0, maka output Q akan set (Q = 1).

- Jika J = 1 dan K = 1, maka output Q akan toggle (berubah dari 0 ke 1 atau sebaliknya).

- Flip-flop JK memerlukan sinyal jam (clock) untuk melakukan perubahan pada output. Sinyal ini mengatur kapan flip-flop akan membaca nilai input J dan K untuk menentukan output.

- Pada gambar, terlihat sinyal clock dikontrol oleh sumber yang berasal dari blok dengan simbol gelombang persegi (X). Sinyal ini memberikan timing untuk perubahan status flip-flop.

T flip-flop bekerja berdasarkan mode Toggle, di mana output akan berubah (beralih antara 0 dan 1) setiap kali ada sinyal clock yang aktif, jika input T (yaitu J dan K) bernilai 1. Berikut adalah penjelasan logika:

- Jika T = 0, maka output Q tetap sama (tidak berubah).

- Jika T = 1, maka output Q akan toggle (berubah dari 0 ke 1 atau dari 1 ke 0) setiap kali ada sinyal clock.

Rangkaian percobaan [klik di sini]

lHTML[klik di sini]

Datasheet NOT [klik di sini]

Datasheet AND [klik di sini]

Datasheet OR [klik di sini]

Datasheet XOR [klik di sini]

Komentar

Posting Komentar